# Lecture Notes in Computer Science 1546 Edited by G. Goos, J. Hartmanis and J. van Leeuwen

# Springer Berlin

Berlin

Heidelberg

New York

Barcelona

Hong Kong

London

Milan

Paris

Singapore

Tokyo

# Prospects for Hardware Foundations

ESPRIT Working Group 8533 NADA – New Hardware Design Methods Survey Chapters

#### Series Editors

Gerhard Goos, Karlsruhe University, Germany Juris Hartmanis, Cornell University, NY, USA Jan van Leeuwen, Utrecht University, The Netherlands

#### Volume Editors

Bernhard Möller

Department of Computer Science, University of Augsburg Universitätsstr. 14, D-86135 Augsburg, Germany E-mail: Bernhard.Moeller@informatik.uni-augsburg.de

John V. Tucker

Department of Computer Science, University of Wales at Swansea Singleton Park, Swansea, SA2 8PP, Wales, UK

E-mail: J.V.Tucker@swansea.ac.uk

Cataloging-in-Publication data applied for

Die Deutsche Bibliothek - CIP-Einheitsaufnahme

**Prospects for hardware foundations** / ESPRIT Working Group 8533 NADA - New Hardware Design Methods Survey Chapters. Bernhard Möller; John V. Tucker (ed.). - Berlin; Heidelberg; New York; Barcelona; Hong Kong; London; Milan; Paris; Singapore; Tokyo : Springer, 1998 (Lecture notes in computer science; Vol. 1546)

ISBN 3-540-65461-5

CR Subject Classification (1998): F.1, F.3, D.2, F.4, B, C.1

ISSN 0302-9743 ISBN 3-540-65461-5 Springer-Verlag Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer-Verlag. Violations are liable for prosecution under the German Copyright Law.

© Springer-Verlag Berlin Heidelberg 1998 Printed in Germany

Typesetting: Camera-ready by author SPIN 10693091 06/3142 – 5 4 3 2 1 0

Printed on acid-free paper

# Preface

This volume, *Prospects for hardware foundations*, explores the theoretical foundations of hardware design. It contains twelve papers on

- (i) mathematical foundations of hardware modelling;

- (ii) models of hardware and dynamical systems; and

- (iii) verification and deductive design of systems.

The papers investigate some of the problems at the heart of our theoretical understanding of hardware systems, their design and their integration with other physical or biological systems. The volume aims to make a conceptual contribution to the theory of hardware and to offer prospects for its development.

Specifically, the articles address theoretical topics, including: stream processing, spatially extended systems, hierarchical structures, integration of analogue and digital models. There are case studies of superscalar processors, the Java Virtual Machine, and biological excitable media. There are design and verification techniques including higher order verification, process algebra, state charts, simulation and reasoning of analogue models. Also there are reflections on constructs for future generation hardware description languages.

This volume is also a scientific memoir of the NADA Working Group, the ESPRIT Basic Research Action 8533. The Action existed over the period April 1994 – October 1997. The Action brought together nine research groups, with interests in theoretical computer science, mathematical logic, formal methods for system design, dynamical systems, and hardware, to pursue a multidisciplinary research programme in the foundations of hardware. It held five general meetings and four specialist workshops, at which the groups met together, with some invited guests, for intensive exchanges; it also sponsored several visits between sites. The introduction to this volume gives further information about NADA; here we describe its origins and scientific purpose.

#### NADA

At the NATO Summer School at Marktoberdorf on Logic and algebra of specification, July 23 – August 4, 1991<sup>1</sup>, the second of the foundations-

<sup>&</sup>lt;sup>1</sup> F L Bauer, W Brauer and H Schwichtenberg (eds.), Logic and algebra of specification, NATO ASI Series F, Vol. 94, Springer-Verlag 1993

# Table of Contents

| Introduction: NADA and NIL The NADA Group                                                                               | 1   |

|-------------------------------------------------------------------------------------------------------------------------|-----|

| I MATHEMATICAL FOUNDATIONS                                                                                              |     |

| Streams, Stream Transformers and Domain Representations J. Blanck, V. Stoltenberg-Hansen and J. V. Tucker               | 27  |

| Ideal Stream Algebra B. Möller                                                                                          | 69  |

| Normalisation by Evaluation U. Berger, M. Eberl and H. Schwichtenberg                                                   | 117 |

| II HARDWARE AND DYNAMICAL SYSTEMS                                                                                       |     |

| Algebraic Models of Superscalar Microprocessor Implementations: A Case Study $A.C.J.\ Fox\ and\ N.A.\ Harman$           | 138 |

| Hierarchies of Spatially Extended Systems and Synchronous Concurrent Algorithms M.J. Poole, A.V. Holden and J.V. Tucker | 184 |

| Towards an Algebraic Specification of the Java Virtual Machine $K.\ Stephenson$                                         | 236 |

| Grid Protocol Specifications J. A. Bergstra and A. Ponse                                                                | 278 |

| The Computational Description of Analogue System Behaviour P.T. Breuer, N. Martínez Madrid and C. Delgado Kloos         | 309 |

# X Table of Contents

# III VERIFICATION AND DEDUCTIVE DESIGN

| Reasoning about Imperfect Digital Systems $K.\ Hanna$                                         | 333 |

|-----------------------------------------------------------------------------------------------|-----|

| F ormal Verification and Hardware Design with State<br>charts $J.\ Philipps\ and\ P.\ Scholz$ | 356 |

| An Exercise in Conditional Refinement $K.$ Stølen and $M.$ Fuchs                              | 390 |

| Deductive Hardware Design: A Functional Approach $B$ $M\ddot{o}ller$                          | 421 |

oriented "Blue Series" of this distinguished institution, there was enthusiastic discussion of hardware systems by people who were studying theoretical aspects of hardware, or were drawn to hardware systems in their work on design and verification. There was excitement about the wealth of problems and the possibilities of solving them. Discussions between John Tucker, Helmut Schwichtenberg, Hans Leiss, Bernhard Möller, Walter Dosch, Carlos Delgado Kloos and Manfred Broy created a common vision of a wide-ranging collaborative study of hardware systems, integrating knowledge of theoretical computer science, mathematical logic, formal methods, and hardware systems. After the Summer School, Jan Bergstra, Viggo Stoltenberg-Hansen and Arun Holden completed the team. Our group wanted to collaborate on research that might

- (i) reveal the essential scientific structure of hardware systems;

- (ii) shape a future generation of hardware description languages;

- (iii) produce new mathematical methods for design and verification;

- (iv) yield interesting theoretical and mathematical problems; and

- (v) perform advanced case studies.

A first proposal for a Basic Research Action in the ESPRIT Programme, in October 1991, was rewarded with polite comments from referees and no funds. Undeterred and keen to collaborate, and with Keith Hanna joining the team, the revised application succeeded: the NADA Basic Research Action Working Group 8533 was awarded in 1993, with one of us (BM) as Coordinator, and held its inaugural meeting in April 1994 at TU Munich.

The aim of the Action was to collaborate in research on new, mathematically sound methods for the description and design of hardware systems. We interpreted the term "hardware systems" very generally to include circuits, architectures and the hardware/software interface. More controversially, we also included the interface between hardware and physical and biological systems.

One goal was the search for a next generation hardware description language having a high level of abstraction and a clean, formally defined semantics. NADA was to analyse the requirements for such an idealised language which was called NIL. Description aspects included general questions of timing, parameterisation and modularisation. The design techniques included verification, deductive design in the small, and structured design in the large.

The goal of the research on modelling hardware and dynamical systems was to elicit requirements on design methodologies and description languages. Architectures, circuits, and emerging new paradigms for hardware systems were studied, as well as various standard technologies, in the

search for unified mathematical models of hardware. Representative case studies were also needed for demonstrations of the developed techniques.

The goal of the research on algebraic and logical foundations for hardware design was to support the above tasks. Appropriate mathematical methods were taken from computability theory, algebraic specifications, higher order algebra, proof theory and process algebra.

In publishing this volume we wish to bring together some of our results and make available our agenda and approach. It is interesting to reflect on progress in the theory of hardware. This volume may be compared with, for example, a volume<sup>2</sup> edited by one of us (JVT), almost ten years ago, on the then current state of hardware foundations. There has been clear progress on most fronts: mathematical tools, semantic frameworks, verification and specification techniques, deductive methods, and complexity of case studies have all been advanced. However, we are far from completing the important scientific task of creating a comprehensive theory of hardware.

#### Acknowledgements

We thank all the participants and guests of NADA for their contributions and support. Each paper submitted for this volume was allocated two referees from within NADA and one referee independent of NADA. We thank the external referees for their criticism: J Baeten, M von der Beeck, D Caucal, W J Fokkink, M Fourman, M Gordon, M Holcombe, T Margaria, A Setzer, D Spreen, Gh Stefanescu, and K Weihrauch.

On behalf of the Group, we thank the European Commission for extending an award for our proposal and granting a five month extension. Working together has brought us forward in our research and led to fruitful interactions. The positive influence of NADA will be felt by its members for years to come.

Finally, on behalf of all the NADA participants, one editor (JVT) would like to thank the other editor (BM) for his outstanding contribution in establishing, sustaining and managing the project: Bernhard, you have our heartfelt gratitude and admiration.

November 1998

B Möller and J V Tucker

<sup>&</sup>lt;sup>2</sup> K McEvoy and J V Tucker (eds.), Theoretical foundations of VLSI design, Cambridge Tracts in Theoretical Computer Science 10, Cambridge University Press, 1990.

# Introduction: NADA and NIL

#### The NADA Group

Abstract. This introductory chapter provides a brief survey of the history and accomplishments of NADA. An extended section presents the recommendations of the NADA Group on future hardware description languages. Finally, the contents of the remaining chapters are briefly introduced. The chapter also lists some references to NADA-relevant work of those NADA members that have not contributed to one of the further chapters.

# 1 A Survey of Esprit Working Group 8533 NADA - New Hardware Design Methods

#### 1.1 Aims and Scope

The topic of NADA was research on new, mathematically sound methods for the description and design of hardware systems. The term "hardware systems" was interpreted very generally to include architectures and circuits, the hardware/software interface and even biological systems. Three major subtopics were identified within the Inaugural Meeting in April 1994:

- modeling:

- hardware description languages and design techniques;

- foundations.

The goal of the research on modeling was to elicit requirements on design methodologies and description languages. It included studying architectures, circuits and emerging new paradigms for hardware systems, as well as various standard technologies.

The investigations around NIL ("NADA Integrated Language"), a fictitious next generation hardware description language, served to exhibit hardware specification and description concepts at a high level of abstraction for which a clean formal semantics can be given. The requirements on such a language were distilled out of the extensive body of case studies the NADA Group has performed.

The investigated design techniques included verification and deductive design.

The Group was also performing research on the mathematical foundations for hardware design. Appropriate mathematical methods were taken from computation theory, higher order algebra, proof theory, relation algebra and timed process algebra.

#### 2 The NADA Group

#### 1.2 The NADA Participants

We give a table of the NADA participants as of the official project termination in October 1997. The University of Augsburg served as the Prime Contractor with B. Möller as the Coordinator of the Group. The responsible researcher at each site is marked by italic type font.

| University of Amsterdam         | Jan A. Bergstra, Alban Ponse       |

|---------------------------------|------------------------------------|

| University of Augsburg          | Bernhard Möller                    |

| University of Kent              | F. Keith Hanna                     |

| University of Leeds             | Arun V. Holden                     |

| Medical University of Lübeck    | Walter Dosch                       |

| University Carlos III of Madrid | Carlos Delgado Kloos, Peter T.     |

|                                 | Breuer, Natividad Martínez Madrid, |

|                                 | Luis Sánchez Fernández             |

| Ludwigs-Maximilian-University   | Helmut Schwichtenberg, Hans Leiss, |

| Munich                          | Ulrich Berger                      |

| Technical University Munich     | Manfred Broy, Peter Scholz,        |

|                                 | Jan Philipps                       |

| Royal Technical Highschool      | Karl Meinke                        |

| Stockholm                       |                                    |

| University of Wales Swansea     | John V. Tucker, Neal A. Harman,    |

|                                 | Matthew J. Poole, Karen Stephenson |

| Uppsala University              | Viggo Stoltenberg-Hansen           |

Most of these participants have been with the Group from the very beginning. Some of them have moved locations during the duration of NADA: the Spanish partners switched from the ETSIT Madrid to their current university, W. Dosch left Augsburg to move to Lübeck and K. Meinke changed from Swansea to Stockholm. Earlier participants were J. Brunekreef at Amsterdam, M. Fuchs at TU Munich, B.C. Thompson at Swansea and P. Abdullah at Uppsala.

#### 1.3 Main Overall Achievements

The first year was dominated by case studies in description and modeling as well as in verification and deductive design, building on and extending the partners' previous work, mainly concentrating on aspects in the small. Concerning NIL, the Group came up with a list of desirable language concepts and explored the possibilities of representing them within the generic theorem prover Isabelle; moreover, the selection of the language concepts was based on their suitability for the methodology of deductive design as employed in various case studies. On the side of foundations, a central theme was the use of streams based on various formal definitions of that concept. Moreover, there were investigations on modeling Synchronous Concurrent Algorithms (SCAs) using process algebra, effective algebras, models of time, tool-independent representation of algorithms and hardware, a framework for hardware-software codesign and technology independent specifications.

The second year was dominated by studies in modeling, on foundational issues and by further case studies. Concerning language issues, the Group started exploring MHDL for possibilities of serving as a basis for NIL. It turned out that many of the concepts exhibited in Year I were already accommodated there, although a coherent semantic framework was missing.

The third year significantly advanced the state of the art in the areas of modeling, deductive design and foundations. Concerning language issues, there was a severe backdrop imposed on the Group: the development of the language MHDL it had started exploring as a possible basis for NIL was abandoned. Meanwhile a new development is under way: SLDL (System level description language). However, this language is still in its requirements definition phase and so could not be used within the project duration. The Group's recommendations on NIL are detailed in Section 3.

### 1.4 Workshops and Conferences

Next to the NADA Inaugural Meeting in April '94, hosted by TU Munich, the formal milestones for NADA were the three Annual Meetings, organized by Swansea in March 1995, Uppsala in April 1996 and Madrid in April 1997, as well as the Final Meeting, organized by Lübeck in September 1997. In between these there were specialist workshops, viz. one on first case studies and an exploration of language concepts, organized by Madrid in October 1994, one on the central topic of streams, organized by LMU Munich in October 1995, and one on further case studies and language issues, organized by Amsterdam in October 1996.

Besides these NADA-specific meetings, NADA partners were also concerned with the organization of related conferences.

A lot of important material in the realm of deductive design was presented at the *Third International Conference on The Mathematics of Program Construction*, Kloster Irsee, Germany, July 17-21, 1995 [19,20], which was chaired and organized by NADA member B. Möller and partially sponsored by NADA.

On the side of foundations, two major events were the Second and Third International Workshops on Higher Order Algebra, Logic and Term Rewriting. The former of these took place at Paderborn, Sept. 21-22, 1995 [6], sponsored by the EACSL and with NADA members K. Meinke and B. Möller in the organizing committee. The latter of the workshops was held in conjunction with ALP (Algebra and Logic Programming) Southampton, Sept. 2–5, 1997 [8]. It was sponsored by the EACSL, and NADA members K. Meinke and B. Möller were again part of the organizing committee.

Finally, the NADA group had the opportunity to present its work to a broad audience at the *Third Annual NADA Meeting* held in conjunction with the conferences CHDL/VUFE/LCMQA '97 at Toledo, 20–25 April, 1997, and organized by NADA member C. Delgado Kloos. In particular, a tutorial on four central threads of NADA research was presented. All this was well-received and gave NADA considerable international visibility.

# 2 Project Achievements of the Individual Sites

#### 2.1 Amsterdam

Amsterdam's participation in NADA triggered a lot of design and specification activity, ranging from refinement of the concept *early input* to design and application of Grid Protocols. Early input is a way of passing values between concurrent processes; it is primitive to formalize and used to model stream processing. Amsterdam's participation in NADA was driven by two general goals:

- To find simple and adequate primitives, and elegant algebraic methods to model data transfer between concurrent processes, and

- To give a process algebraic account of applications that are relevant to NADA, viz. the modeling of hardware phenomena, and development of respective analysis techniques.

As an example we mention the Amsterdam work on SCAs (Synchronous Concurrent Algorithms) as developed by Tucker et al. The following achievements of Amsterdam's participation in NADA can be distinguished:

- A better understanding of scientific work done elsewhere. This applies in particular to the modeling of hardware and other concurrent phenomena in which parallel input/output is a major ingredient.

- Much more focus on a systematic treatment of data manipulation in process algebra, as exemplified by the early input concept. Traditionally, process algebraic modeling often concentrated on operational aspects of concurrency, and treatment of data manipulation (by processes) was ad hoc or left implicit.

- Distinguishing primitives for file-transfer; further research on an algebraic treatment of (concurrent) assignment is being undertaken.

- A close observation of the development of  $\mu CRL$  ("process algebra with data") at CWI.

- Research on process algebra with recursive operations, such as binary Kleene star and nesting, in particular in combination with early input and valuepassing.

## 2.2 Augsburg

The focus of the work at Augsburg has been on the method of *Deductive Design*, i.e., on the systematic construction of a system implementation, starting from its behavioural specification, according to formal, provably correct rules. The main advantages of this approach are:

- The resulting implementation is correct by construction.

- The rules can be formulated schematically, independent of the particular application area, and hence can be re-used for wide classes of similar problems.

- Since the rules are formal, the design process can be assisted by machine.

- Implementations can be constructed in a modular way, with emphasis on correctness first and subsequent transformation to increase performance.

- The formal derivation also serves as a record of the design decisions taken and hence is an explanatory documentation. Upon modification of the system specification it eases revision of the implementation.

This paradigm has successfully been applied to sequential and, to a lesser extent, also to parallel programs. Since hardware consists of "frozen" programs, it is an obvious idea to apply this method to hardware design. A large amount of work in this area has been done by M. Sheeran and others.

The major novel ingredients and achievements in the Augsburg work are the following:

- specification at the level of predicate logic, not necessarily algorithmic yet,

- a clearer disentangling of the abstract idea of an algorithm from the concrete layout that realizes it,

- in particular, introduction of wiring operators in a late stage of the derivations, thus avoiding a lot of burden and clutter,

- a simpler approach to retiming that avoids the concept of anti-delays,

- in the asynchronous case a strongly algebraic approach to streams, notably to questions about fairness.

While the first two items had been established already in the CIP group to which NADA members B. Möller and W. Dosch belonged, the latter three items were elaborated within the NADA project.

The case studies include many of the IFIP WG10.5 Benchmark Verification Problems [7]. Next to dealing with basic combinational and sequential circuits, a very simple treatment of systolic circuits was achieved. Finally, concerning higher-level hardware concepts, an easy formal account of pipelining became possible.

Special emphasis was laid on parameterization and re-usability aspects.

In the synchronous case, a major breakthrough was the switch to formalizing the specifications and derivations using the functional programming language *Gofer*, a subset of *Haskell*. The polymorphism of this language allows the use of Ştefănescu's network algebra and other algebraic laws both at the level of combinational and sequential circuits. Also fixpoint induction and related proof principles can be applied directly. Moreover, many derivations can be performed in a polymorphic way abstracting from concrete applications and hence achieving much better re-usability.

In the asynchronous case, the algebraic basis has been consolidated. This thread of work concerns more algebraic ways of specifying, reasoning about and transforming descriptions of (sets of) streams. Particular emphasis is laid on the use of regular algebra in describing stream patterns, notably in connection with questions of fairness. This algebraic approach has also been tied in with other specification formalisms such as temporal and modal logic.

#### 2.3 Kent

The work undertaken at Kent has focused on two themes: the use of dependent types in specifications for digital systems and in extending formal verification from the digital domain towards the analog domain.

The motivation for using dependent types (loosely, types that are parameterized by values and/or other types) for formal specification is that they offer both greater expressiveness and greater generality. During the course of the NADA project, Kent have:

- Carried out an in-depth investigation of the use of dependent types in specifying and in formally verifying complex systolic array architectures;

- Shown how it is possible to capture, within a formal theory, the interrelation between the structural and the behavioural aspects of a circuit. Circuits are treated as typed graphs and their behavioural specifications as predicates. The key difficulty that has to be overcome is that, in a structural description, the types of ports have to be treated as values whereas, in the behavioural description, they appear as types. Using dependent types, it was found possible to devise a sufficiently expressive type for interfaces that guaranteed the consistency of structural and behavioural specifications. The approach was demonstrated using Veritas, an implementation of a dependently-typed higher-order logic.

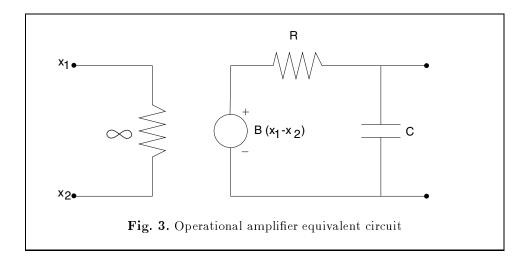

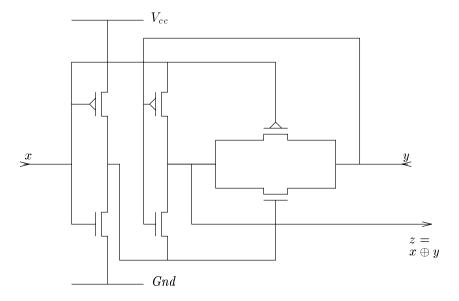

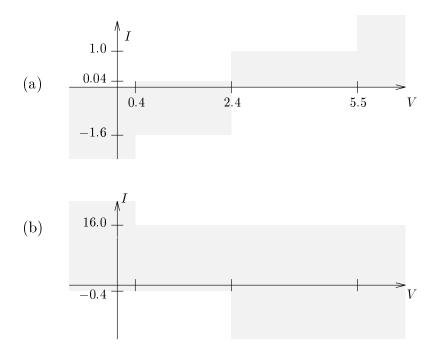

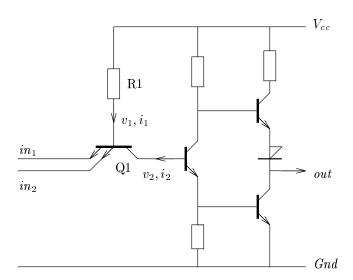

The motivation for extending formal specification and verification techniques from the digital domain towards the analog domain is that, in practice, significant sections of a digital system often have to be designed at the analog electronics level of abstraction. By doing this, logically redundant signal conditioning and buffering stages can be eliminated, leading to circuitry which can be up to an order of magnitude faster, and with lower power consumption, than the corresponding circuitry designed (in terms of gates and flipflops, etc) at the digital level of abstraction. During the course of the NADA project, Kent have:

- Demonstrated how, using higher-order logic, the behavioural characteristics

of typical electronic components (transistors, diodes, resistors) can be specified in terms of analog voltages and currents.

- Shown how the behavioural specification of an electronic circuit (for example, one that uses pass-transistor logic) can be inferred from the analog specifications of the component parts and their interconnections and how specifications at the analog and digital levels are related.

- Devised and implemented a decision procedure that, given a description

of an analog circuit and behavioural specifications of its component parts,

determines whether it correctly implements a given behavioural specification.

Kent believe that this work is likely to impact strongly upon the design of future generations of mixed-level hardware design languages which, at present, lack rigorous foundations.

#### 2.4 Leeds

The focus of the work at Leeds has been on the development and evaluation of case studies, based on biomedical applications, that are practical illustrations of what current problems exist in the computational modeling of complicated, highly structured, spatially extended systems that are represented mathematically by different classes of models - cellular automata, coupled map lattices, coupled ordinary differential equation lattices, and partial differential equations, and that interact with data streams. The main idea of the approach is to use the theory of synchronous concurrent algorithms as a framework within which different types of model are embedded, and can be coupled. The advantage of this modular approach is that newer generation models can readily be incorporated, and the framework is applicable to modeling a wide range of hierarchical, structured system, not just the case studies, based on cardiac muscle, arryhthmias, and their control. The principal results of the Leeds work have been:

- The development of a family of partial differential equation models for different normal and pathological cardiac tissues, and the use of these models to simulate cardiac arrythmias.

- The design of a novel means of controlling re-entrant cardiac arryhthmias, and the evaluation of its practicability.

- The development of a geometric, anisotropic model for the ventricles of the heart, and the coupling of this geometry with simple (coupled map lattice, simple ordinary differential equation models) of excitability and with partial differential equation models.

- The development of a formal approach, within the theory of synchronous concurrent algorithms, for coupling and verifying the above models.

- The application of the same approach to other biological systems neural nets, and oceanic plankton population dynamics.

This approach has been primarily in collaboration with the Swansea group, and has led to extensive funding from UK research council and medical charities, in the applications of these models to clinical problems. It has also led to UK funding to continue the collaboration with the Swansea group.

#### 2.5 Lübeck

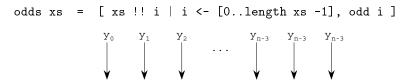

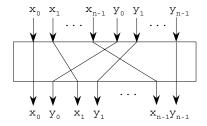

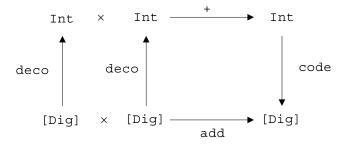

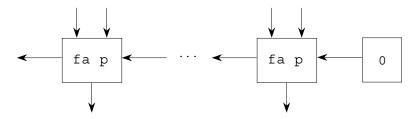

The work in Lübeck concentrated on deductive design — both in the area of hardware and software [5]. This methodology aims at systematically deriving a system implementation from its behavioural specification following sound transformation rules. The derivation documents the design decisions and guides the redesign upon changing requirements. Within a structured design methodology, one initially abstracts from layout and timing issues and concentrate on algorithmic design principles. Synchronous descriptions are based on the algebra of finite sequences modeling the linear succession in space or in time; asynchronous descriptions employ stream processing functions. The major contributions in the work of Lübeck consist in

#### 8 The NADA Group

- isolating and formalizing important design steps [3],

- abstracting characteristic design patterns from specific case studies,

- deriving standard implementations for iterative and tree structured networks using higher-order functions,

- reasoning about ordered streams by set abstraction [4].

For a class of digit recurrence algorithms, W. Dosch has derived different implementations as combinational and sequential circuits in a schematic way. This class of iterative circuits was then generalized to tree structured networks originating from cascade recursive functions. The derivations are parameterized supporting their re-use in different applications.

#### 2.6 Madrid

The Madrid work has been concentrated in three main areas. The first area is the semantics of hardware description languages, chiefly in connection with the formalization of VHDL and the development of specification, refinement and verification calculi for that language and real-time systems in general. Secondly, Madrid have been working with the specification language LOTOS. They have produced methods for designing hardware systems and generating VHDL code automatically from the design. Thirdly, Madrid have been researching in the area of codesign also using LOTOS as the system description language.

Madrid have given several presentations to the Group about the last two areas and have been actively developing the first area within the project itself. Participation in NADA has been specially useful to Madrid in the further development of their logic for real-time system design from their approach to VHDL semantics. With regard to the latter, Madrid have debugged the refinement calculus of VHDL, finally proving it to be complete with respect to their formal semantics for the language. Madrid have also taken the opportunity to investigate the problems of design in non-discrete regimes using their formalisms and those of others. The operational amplifier has been a particularly instructive example of an analog device operating in continuous time. From their attempts to describe it, Madrid have concluded that compositionality under these regimes derives from the constraints on a system and not from the solutions to (subsets of) those constraints. If one tries the latter approach one runs into problems with causality requirements. As a result of these investigations, Madrid have been able to suggest a semantic model for the analog extension to VHDL (now accepted by the IEEE), developing a prototype implementation.

#### 2.7 LMU Munich

LMU have worked on a variety of subjects all subsumable under the heading 'applied proof theory'. This was done in conjunction with the development of an interactive prover MINLOG, well suited to the purpose and, in particular, for hardware verification and development. Most notably U. Berger and M. Eberl have been working on NADA-related questions.

LMU work in the area of program extraction from classical proofs. To this end they apply H. Friedman's A-translation followed by a modified realizability interpretation. However, to obtain a reasonable program it is essential to use a refinement of the A-translation introduced in Berger/Schwichtenberg 1995. This refinement makes it possible that not all atoms in the proof are A-translated, but only those with a "critical" relation symbol. Yannis Moschovakis suggested the following example of a classical existence proof with a quantifier-free kernel which does not obviously contain an algorithm: the gcd of two natural numbers  $a_1$  and  $a_2$  is a linear combination of the two. In that example only the divisibility relation  $\cdot|\cdot$  turns out to be critical.

In addition, LMU worked on case studies in hardware description and verification, among which is the min/max-example from the IFIP WG 10.5 Hardware Verification Benchmarks [7].

#### 2.8 TU Munich

In the past years, the design methodology Focus for distributed systems has been developed at TUM. As the original intention of Focus was to describe software systems, the NADA project has been a unique opportunity to verify to which extent Focus is applicable for the specification of hardware, too. To achieve this, a number of case studies, like the formal development of a production cell, a distributed min/max component, interfaces, modulo-n counter, and the Alpha  $AXP^{TM}$  shared memory have been carried out using Focus.

Apart from these case studies, which have shown that Focus is indeed suitable for the description of hardware oriented systems, it also turned out that Focus provides a mathematical framework for defining a formal semantics for hardware description languages like VHDL and system level languages like Statecharts. Furthermore, it was proven that Focus is not only appropriate to describe pure software or hardware components but in addition can be used to specify mixed hardware/software systems, i.e. can serve as a formal foundation for Hardware/Software Codesign.

#### 2.9 Stockholm

Foundations of Hardware Specification K. Meinke has investigated the foundations of hardware specification using higher-order algebra. Roughly this corresponds with the equational fragment of many-sorted higher-order logic, where higher types are function types. Thus it is related to Church's system of finite types. This framework is natural for hardware description since it allows the direct representation of hardware devices as stream transformers. This observation has also been confirmed elsewhere, e.g. the HOL community. Significant achievements in this area have been:

- An exact characterization of the specification power of higher-order equations [14]. Earlier work on this problem was published in [12]. This power was shown to be  $\Pi_1^1$ , thus it properly includes the arithmetical hierarchy.

#### The NADA Group

10

Furthermore, the expressive power of the hierarchy of specifications (second-order, third-order, etc.) collapses to second-order. In this sense, (quantifier free) second-order equational logic is slightly more powerful than first-order arithmetic.

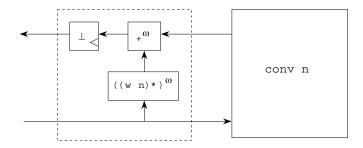

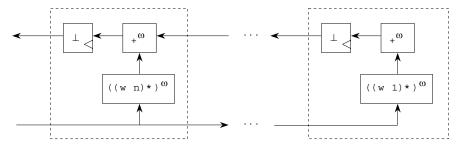

A proof theory for higher-order equations which exactly characterizes the case where higher-order equational reasoning is reducible to first-order equational reasoning through the existence of normal form proofs for higher-order equations. This result makes use of a particularly interesting topology on higher-order algebras which seems to capture a definition of observational equivalence for higher-order operations (e.g. stream transformers). Case study research [16] on Kung's systolic convolution algorithm found this to be a useful result for theorem proving and hardware verification.

Practical Case Studies Together with L.J. Steggles, K. Meinke studied some well known hardware algorithms in order to gain insight into their specification and verification requirements. These included a typical systolic algorithm (convolution) and a typical dataflow algorithm (Hamming Stream). The convolution algorithm lead to fundamental insights in the proof theory of verification for systolic algorithms (see above). The dataflow algorithm revealed the power of higher-order algebra for semantical verification.

L.J. Steggles extended the theory of higher-order algebraic specification to transfinite types, and showed that this formed a suitable framework to capture the parametricity of families of hardware algorithms [22]. He also developed a theory of parameterized higher-order algebraic specifications, which allowed taking advantage of the polymorphism inherent in the convolution algorithm to simplify the specification [23].

K. Meinke investigated the impact of the proof theory of higher-order equations on higher-order equational theorem proving, and verification of hardware by means of term rewriting in [13].

Software Tools Together with B.M. Hearn, K. Meinke designed and implemented a tool for parsing and executing higher-order algebraic specifications by rewriting of terms and types. This tool was based on earlier published research of K. Meinke. The tool and its input language is called ATLAS (A Typed Language for Algebraic Specification) and is based on many-level algebraic specifications, which can be used for equational specification both of data and types (by means of type equations). ATLAS [9] is implemented in C under UNIX and has a Motif graphical user interface. ATLAS was used to specify and verify hardware algorithms, as well as other case studies, including order-sorted, polymorphic and recursive types.

The research on ATLAS was also taken further by E. Visser at the CWI Amsterdam (outside the NADA project).

#### 2.10 Swansea

further.

Algebraic Models of Microprocessors Work on microprocessor modeling has progressed from basic representations of simple processors, at the level of the programmer, through models of microprogrammed implementations, to models of advanced processor implementations. In addition, considerable attention has been given to the problems of verifying the correctness of microprocessor implementations.

At the start of the NADA project, iterated map microprocessor models were restricted to a simple PDP-8-derived example, at the level of the programmer. An implementation of the PDP-8 was developed, and in parallel a technique was developed for substantially simplifying the process of formal verification. This required that a number of conditions be met, that were trivially satisfied by iterated map models of microprocessors, and their associated timing abstraction functions. A more sophisticated example, with input and output, was then developed. This was based on a standard example, Gordon's Computer.

The substantial body of work on microprocessor representation has been concerned with pipelined, and especially superscalar processors. The problems that these bring are (a) substantially increased complexity of implementations; and (b) a timing model that differs substantially from that of the programmer's level model, or architecture. Techniques were developed for representing superscalar microprocessors, and existing correctness conditions were modified. Work continues on developing techniques for simplifying the verification of superscalar processors.

An Algebraic Framework for Linking Program and Machine Semantics During the period 1994–1997, K. Stephenson and J.V. Tucker constructed an algebraic framework in which the process of executing a high-level program can be described at the level of hardware. There are many layers of abstraction involved between these two extremes. Each layer of the hierarchy consists of an algebraic specification for the semantics of the language at that level. To produce specifications for each layer requires the syntax and a semantic mapping of the language to be defined. In addition, to compare levels of the hierarchy and to define the relative correctness of levels to each other, these layers are structured

General methods of defining syntax are based on the notion of *filtering* context-free supersets to produce algebraic specifications of non-context-free languages. This work is set against a background of research into the relationship between context-free grammars and closed term algebras.

An operational model of semantics is used in which the sequences of states produced by the execution of programs are explicitly clocked by time. This enables computable models of operational semantics to be developed and hence algebraically specified. In particular, this provides an algebraic approach to structural operational semantics of high-level languages. The approach is also applicable to the semantics of low-level languages; this work is set against a

background of research into machine semantics developed by J.V. Tucker and N.A. Harman within NADA.

In addition, each layer is structured so that the specifications have a common signature. This allows the process of compilation between the layers to be expressed as a homomorphism. Correctness of one level of the hierarchy with respect to another can then be stated in terms of commutative diagrams. This work is set against a background of research in algebraic semantics.

It has been shown, to deal with concepts at a higher level of abstraction, that the act of proving correctness can be reduced to establishing the correctness of the commutative diagram before execution (trivially) and at the end of the first time cycle. As these stages do not require structural induction to be used, this both dramatically reduces the work required, and also makes the process feasible for mechanical checking by a suitable theorem prover.

The first two levels of this hierarchy are specified and are (manually) shown to be correct relative to each other for a non-trivial case study of a simple while programming language and a very abstract machine-level language. This framework is now being extended to deal at lower levels of the hierarchy, with the aim of linking the work to that of N.A. Harman regarding the correctness of microprocessors.

SCAs and Dynamical Systems Work by J.V. Tucker and M.J. Poole, in collaboration with A.V. Holden (University of Leeds) has focused on algebraic models of spatially extended computational systems. The theory of synchronous concurrent algorithms (SCAs) has been applied and extended to unify the modeling of a range of different types of hardware system and biological system.

In their biological system applications, Tucker et al. have been primarily interested in coupled map lattice, cellular automaton, neural network, coupled ordinary differential equation and partial differential equation models of spatially extended biological phenomena. They have concentrated on models of electrical phenomena in cardiac tissue. On making discrete approximations of continuous spaces and times, the diverse range of available models of cardiac excitation are all examples of SCAs and may therefore be studied in a unified way, from the point of view of parallel deterministic computation. The notion of discrete space and local connectivity in cardiac models corresponds closely with the notion of parallel digital systems; continuous state systems are closely related to analogue computing systems.

Notions of hierarchies of spatially extended systems have been developed within the framework of SCAs. The formal concepts of hierarchy are derived from notions of abstraction and approximation between the structure and behaviour of two SCAs, which in turn are built upon abstractions of time, space and state. The general theory has been exploited in the investigation of systolic algorithms and, especially, of spatially extended biological systems. The concepts of hierarchy have led to the rigorous comparison of the behaviours of mathematically and biologically diverse models of cardiac electrical behaviour that are unified by SCA theory. Further, they have led to the construction of

hierarchical and hybrid SCA models of cardiac activity combining many component models and reconstructing cardiac behaviour at many different, interacting, levels of biological detail.

#### 2.11 Uppsala

The work of the Uppsala site has primarily been concerned with semantical foundations of data types, streams and stream transformers. The main tool used has been the theory of domains. Domain theory arose from generalizations of the theory of recursion and computability in the work of D. Scott, Yu. Ershov and others. Its use in denotational semantics is well known. Uppsala have also considered the use of formal spaces and of certain non-standard models.

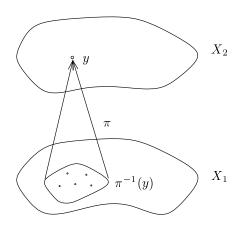

Uppsala's work has been concentrated on considering domain theory as a theory of computation on data types or topological algebras, where approximations are the primary objects. That is, computations are performed on concrete approximations and the results are then transferred to ideal or non-concrete elements (the elements of the considered topological algebra) via a limit process. A domain captures this idea well. The method used is that of domain representability for topological algebras, developed by V. Stoltenberg-Hansen and J.V. Tucker starting in 1985. This general technique was applied to the processing of streams with discrete and continuous time and data.

Another tool useful for the study of computability for topological structures, and for obtaining constructive versions of non constructive theorems such as the Tychonoff or Hahn-Banach theorems, is the theory of formal spaces. Uppsala have made a comparison between this method and the method of domain representability showing their equivalence in certain precise senses for regular locally compact spaces. Uppsala have also found a connection between domain theory and model theory where saturation plays a key role. The have used this to give a logical presentation of the Kleene-Kreisel continuous functionals.

Finally, Uppsala have considered certain constructive non-standard models which they believe will be useful for foundational questions addressed by the NADA project.

# 3 Observations on NIL — The NADA Integrated Language

In this section we discuss the observations on requirements to future hardware description languages as they have arisen during the NADA work.

#### 3.1 Introduction

The lack of a common hardware description language (HDL) with sound foundations and clear concepts hinder progress in high-level hardware design. HDLs in use support only the lower design level; their semantics are mostly simulator-based and hence awkwardly complex.

#### 14 The NADA Group

NIL is a fictitious next generation hardware description language. This section describes the concepts such a language would contain. It is based on the experience of extensive case studies on specification, verification and deductive design within NADA. Detailed reports on these case studies can be found in the subsequent chapters.

NIL employs concepts at a high level of abstraction and is based on a formally defined semantics. Description aspects include general questions of timing, parameterization and modularization. The design techniques include verification, deductive design in the small and structured design in the large.

During the duration of the NADA Working Group its members were looking at the functionally based language MHDL [21] as a possible basis for NIL. Unfortunately the development of that language was abandoned during the final phase of NADA.

At the same time efforts towards the definition of a System Level Description Language SLDL [24] as a successor to MHDL were set up. Currently this language is in its requirements definition phase. Many of the aims put forward by the SLDL committee fall well in line with observations by NADA. Therefore we shall freely quote the current SLDL requirements document to underline our views. Such citations are marked by slight indentation and a slanted type font. The mission statement of the SLDL effort is as follows:

To support the creation and/or standardization of a language or representation, or set of languages or representations, that will enable engineers to describe single and multi-chip silicon-based embedded systems to any desired degree of detail and that will allow engineers to verify and/or validate those systems with appropriate tools and techniques. The languages or representations will address systems under design and their operating environment, including software, mixed-signal, optical, and micro-electronic mechanical characteristics.

The SLDL requirements document goes on to say:

Note that the mission statement does not necessarily require a specific language; a set of languages, or a meta-notation, or something of this sort is perfectly acceptable as long as it meets the requirements set forth in this document.

This agrees very well with the actual road the NADA work took: the different groups have developed various formalisms, each suited to a particular problem domain. Due to lack of manpower, the complete design and definition of NIL could not have been achieved within NADA anyway.

## 3.2 Central Requirements on NIL

This section surveys the central requirements on NIL as they were identified within NADA. We deem the concepts essential for structured hardware description and design; however, they are only incompletely realized in existing HDLs such as VHDL, CIRCAL, ELLA, LTS. The reader is invited to compare the requirements with the SLDL ones.

**Scope** NIL is a general purpose language supporting the description of different types of hardware at several levels of abstraction, in particular, the behavioural, the structural and the layout levels.

**Declarative Style** NIL should have a clean declarative core which supports realization-independent behavioural specifications. Declarative hardware description abstracts from layout structure and computational process to functional behaviour.

Semantic Coherence NIL must provide a coherent semantic framework which, in the design, allows passing smoothly from specifications through component descriptions to concrete realizations. In particular, There have to be constructs for expressing non-functional aspects (resource bounds), among which are the allocation of computations both in space and time. The semantic model must coherently cover continuous and discrete notions of time as well as a notion of space.

Structuring and Parameterization NIL must support the decomposition of complex systems into subsystems in all design phases. For this purpose, it has to offer flexible component descriptions with clear interface specifications.

It must allow hierarchical design, large-scale parameterization and re-use of components.

**Design Correctness** NIL must support establishing the correctness of a design by formal methods. It has to encourage a modular and stepwise design process, based on sound notions of refinement.

In particular, the semantic model must allow concise transformation and verification rules that support deductive design and design verification. The refinement and abstraction concepts comprise timing, structure and layout. NIL supports the analysis of designs by providing rules how to infer properties from descriptions.

Extensibility NIL must be extensible so that users can tailor it to their particular needs. Such language extensions may capture specialized types of hardware (synchronous circuits, combinational circuits, associative memory) or particular realization levels (register transfer level, CMOS level).

The extension layers have to be explained in terms of the kernel language. In this way the language itself has a modular structure. This scheme has profitably and successfully been applied to the language CIP-L [1].

Tools and Graphics NIL has to be designed such that it interfaces with well-established tools such as VERILOG and VHDL simulators and compilers. In particular, NIL must designate operational sublayers for rapid prototyping, simulation and compilation. NIL also offers a standard interface to graphical tools supporting the visualization and visual manipulation of designs.

Use in Engineering and Education To gain wide acceptance, NIL cannot involve sophisticated concepts. The semantics and the type system should be as simple as possible. For the engineer, NIL must combine manipulative fluency with intuitive comprehension. For education, it should serve as a conceptually well-formed and clean vehicle for teaching hardware design methods. Moreover, NIL should attempt to bridge the gap between software and hardware design.

Let us conclude this section by another quotation from the SLDL document:

The key activities of systems design include feasibility studies, concept selection, product selection and architectural (high-level) design. System design typically includes the following capabilities (as described in the section below on SCOPE):

- Several levels of abstraction that are essential to support feasibility studies and concept selection.

- Modularity in both functional and structural design to support product selection.

- Verification, including analyses such as simulation modeling.

- Provision for constraints and back annotation from downstream design stages.

- Test planning to support architectural design.

#### 3.3 Survey of NIL Core Concepts

Approach The approaches to formalization of hardware aspects used by NADA members are based on predicate logic and concepts from functional programming. Therefore it is natural that the core of NIL should essentially be a suitable fragment of logic and typed  $\lambda$ -calculus.

The core should stay close to standard algebraic and functional specification, i.e., use equational many-sorted logic, as long as possible. This will motivate the recommendations below on the various choice options.

An important question is whether to use total or partial functions as operators. Differing from the CoFI initiative [2], for simplicity NIL uses total functions because they lead to a much easier logical framework. Partial functions can be simulated through suitable totalization or by simulating relations by set-valued functions.

**Basic Concepts** The basic entities involved in any component are *data*, *time* and *space*.

Based on these, *streams*, also known as *traces* or *waveforms*, record the temporal succession of data at a given *input or output port*, whereas *states* record for each point in space and each time a data value. The computation by a module at a location in space is described by a *stream transformer*.

**Data** The data involved in the circuit level of hardware description mostly are of a very simple kind, such as Booleans or more refined logical values. At higher levels, particularly at the architecture level, also more involved data structures are needed. While equational axiomatizations using a generation principles are well-known, it may be advantageous to include certain standard data type constructors such as sums or products to allow recursive data types in the form known from functional programming languages.

All these data structures are discrete. It has to be determined whether continuous data make sense and how they would be described. This aspect certainly is a core concept.

**Time** NIL must include various concepts of time. Some options are

- discrete vs. continuous time;

- time with and without a starting point;

- linearly vs partially ordered time.

Discrete time usually is isomorphic to (an interval of) the natural numbers. It is easily axiomatized using an enumeration function or inductive definition.

Continuous time cannot be enumerated. It is best axiomatized using an order relation. This suggests use of predicate symbols other than just equality. Non-discreteness is axiomatized e.g. by requiring

$$\forall x, y : x < y \Rightarrow \exists z : x < z < y$$

,

which involves an existential quantifier. This can be avoided by introducing a Skolem function  $between: Time \times Time \rightarrow Time$  with the axiom

$$x < y \Rightarrow x < between(x, y) < y$$

.

Completeness is even worse, since it requires quantification over subsets to talk about infima/suprema. By the increasing importance of hybrid systems, however, continuous time cannot be neglected. For many hardware purposes discrete time will suffice, though.

Linear time is adequate for modeling systems with a global time. For asynchronous systems it may be advantageous to use a partial ordering of time.

Space Space serves to locate single subcomponents, which are entities with a well-defined extent. Hence the concept of continuous space is not relevant for NIL. Discrete space can be described via suitable enumeration functions or, in a more structured way, by inductive definition.

The elements of the space domain will be called *locations*.

For the description of placement and topologies the space domain needs to be equipped — in increasing degree of precision — with a neighbourhood relation, coordinates or even a metric.

**Timing Disciplines** Once a notion of space has been fixed, we can also talk about global or local time. For global time, a single sort Time is sufficient. To describe local time, one either needs to view Time as a sort constructor parameterized by elements of Space, or to reflect locality by retimings between the subcomponents.

For various retiming concepts see Lustre, Signal, Ruby as well as the SCA framework.

**Connectivity** The neighbourhood relation between locations can also be given by a function  $Nbd: Space \times Time \rightarrow Set(Space)$  that assigns to each point a neighbourhood, i.e., a set of other points. Depending on whether the underlying relation is symmetric, this models bi-directionality or uni-directionality.

The neighbourhood relation may even be time-dependent. This way one can describe dynamic structures as used e.g. in on-the-fly programming of FPGAs.

Another issue about connectivity is the treatment of channels. Options here are

- explicit naming/renaming/hiding of channels;

- use of special constants for interconnection networks.

Case studies have shown that both should be accommodated. Since they are inter-definable it is to be determined which option should go into the core.

Streams and Waveforms The options here are total vs. partial streams. Total streams are simply functions from time to data. Partial streams stop after a certain time. Among these one finally can distinguish between complete and incomplete. Total streams fit in nicely with the decision to use total operations.

Axiomatizations of partial streams are less direct in this setting. Possibilities are:

- 1. use a dummy element and inflate each partial stream to a total one that constantly yields the dummy after a certain initial part;

- 2. use higher-order concepts to distinguish the set of all (proper and improper) intervals of the time domain and have streams as functions from these intervals to data:

- 3. use domain-theoretic notions to characterize total streams as limits of the partial ones.

Of these, the first is the simplest.

As soon as continuous time is used, streams should better be called waveforms. For them, option 2 for describing partial waveforms becomes more interesting, since then quantification over subsets of the time domain are used anyway.

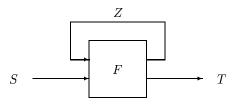

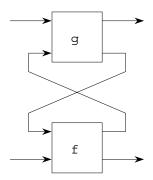

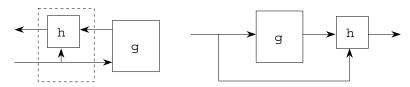

**Stream Transformers** This is probably the easiest concept: a stream transformer is a function from (tuples of) streams to (tuples of) streams. This is independent of all choices for the underlying domains of time, data and streams.

This notion suggests the use of higher types. As Möller [17, 18] and Meinke [11] have shown, this fits in well with equational logic, even if the axiom of extensionality is required to hold. Higher types would also easily accommodate a full typed  $\lambda$ -calculus, which is convenient in many formulations.

For the stream transformers further properties, such as monotonicity, continuity or causality, may be required.

Non-Determinacy There is quite a ramification in how NADA members model non-determinacy (if at all). The concepts used here are, in increasing semantic complexity,

- sets of streams (traces);

- sets of stream transformers;

- CCS/CSP-like processes.

Whereas the Amsterdam partners are using their well-established process algebra, essentially a first-order equational theory, the other two approaches heavily use higher-order concepts.

Uses of non-determinism in hardware description are e.g. modeling the accesses to a bus structure and handling of I/O events.

State Certain components, such as sequential circuits, depend on an internal state, whereas others, such as combinational circuits, do not. Depending on whether a component employs global or local time for its subcomponents, the state will be global or locally distributed. A global state can be modeled by a function  $State: Space \times Time \rightarrow Data$ , where Time is the global time domain. If streams are simply functions from Time to Data, one can, by currying, equivalently use  $State: Space \rightarrow Stream$ .

Another way to model states is to use a stream of states in a feedback loop. In components with local time, local streams may be used to describe the local states. However, this would mean that *Stream* now needs to be a parameterized data type constructor, and the *State* function now needs to involve a dependent type:

$$State: (x: Space) \rightarrow Stream(Time(x), Data(x))$$

.

In components with global state, the stream transformer at each point in space may or may not depend on that state.

**Architecture** The *architecture* of a component is described by its connectivity, the timing discipline (global or local), the global state function (if any), the stream transformer or process at each location and the *parallel composition* of all these. If the definition of parallel composition is taken general enough it also comprises sequential composition and feedback.

**Systems** A system is the parallel composition of components. It will again involve a notion of space to locate the components, and a notion of connectivity. To allow hierarchical structuring, it would be most simple and coherent to view systems again as components. However, then parallel composition of

stream transformers, which model the computation in subcomponents, has to be somehow unified with the "parallel composition" of algebras, which model the components.

In any case, there have to be concepts for expressing modularization, i.e., composition/decomposition of systems and hiding of internal structure; the semantics has to be compositional w.r.t. the correct implementation relation.

Possible Extensions Here we first list a few concepts that have proved valuable in some NADA case studies, but entail a certain semantic complexity, so that it is unclear whether they should be part of overall NIL. These are, above all, parameterization of types, polymorphism and dependent types. While each of these topics is well-understood by itself, their combination leads to problems with type checking that have not yet been resolved.

Another topic are formal descriptions of interfaces. While purely syntactic descriptions exist in many programming languages, in the overall line of NADA NIL would have to contain interface descriptions as "first-class citizens" that can be freely manipulated and formally reasoned about. Experiments have been performed to describe interfaces in the form of higher-order logic expressions, but no conclusive solution has been found.

The second group of concepts that would enter, but for which no case studies have been performed within NADA, are non-functional aspects, such as speed and size of components. Examples of this are the clock calculus in Lustre/Signal (which is used also for determining whether a stream-based specification can have a realization in bounded memory at all) or Skillicorn's cost calculus for parallel algorithms on lists.

#### 3.4 Reasoning

One purpose of a formal system description is to allow precise reasoning about it. To this end, a precise formal semantics of the description language has to be given. A central notion is that of one component correctly *implementing* another.

Concepts of Correctness There are well-studied implementation relations both for the algebraic and the logical/functional/relational views of systems. In the presence of non-determinacy, the implementation must allow behaviour refinement (reduction of non-determinacy and/or increase of "definedness"). Further essential concepts are abstraction from layout/topology, interface refinement and data refinement. Moreover implementations via retimings have to be taken into account.

**Reasoning Tools** Since one of our basic aims is to keep the underlying logic as simple as possible, also our reasoning tools should be somewhat restricted:

- equational reasoning using the equational axioms or fixpoint properties of recursively defined entities;

- in the case of refinement, inequational reasoning using the refinement relation and monotonicity;

- induction principles, viz.

- structural induction and

- fixpoint induction for recursive definitions (using both least and greatest fixpoint semantics);

- uniqueness of the solution of certain fixpoint equations.

**Design Verification** In verification, one constructs the implementation by some independent proceeding and afterwards tries to show that it correctly implements the specification.

The methodical advantage of this is that one gives two views of a system; if they can be correctly related, this increases confidence in the overall formalization.

Relevant techniques here include model checking and equational reasoning over algebraic specifications.

**Deductive Design** In deductive design, one constructs the implementation from the specification by some systematic way. Current methods are stepwise transformation (refinement) or extraction of a program from a proof that the specification can be satisfied.

**Interplay** Verification and deductive design may be combined fruitfully. For instance, one can develop a library of components using deductive design and use their initial specifications for the verification of larger systems.

# 4 Survey of the Chapters of the Book

The chapters of this book have been grouped according to the main research themes within NADA. Besides the language aspects dealt with in the present chapter, these themes were Mathematical Foundations, Hardware and Dynamical Systems and Verification and Deductive Design.

#### 4.1 Mathematical Foundations

As is clear from the discussion in previous sections, streams and stream transformers are a central topic in formal hardware description. The first two chapters of this part of the book provide mathematical treatments of this subject.

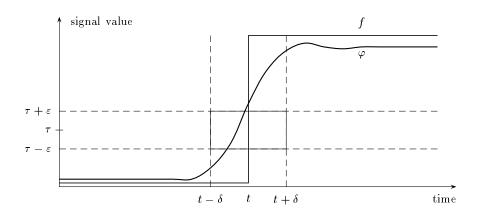

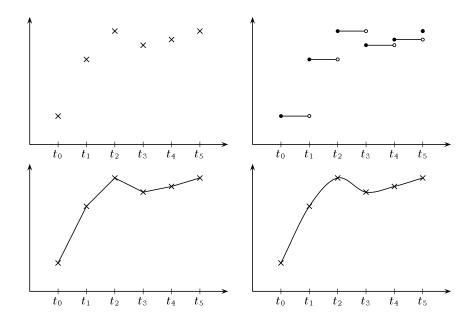

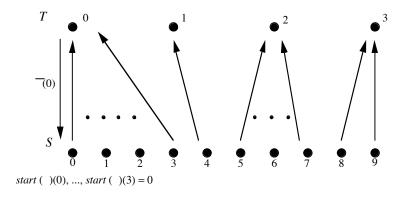

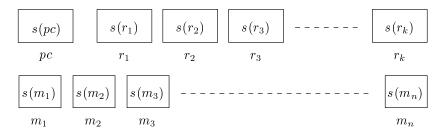

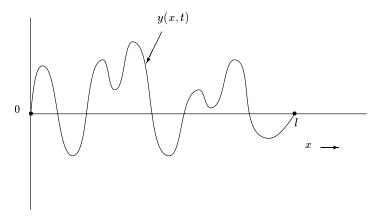

The chapter Streams, stream transformers and domain representations by J. Blanck, V. Stoltenberg-Hansen and J.V. Tucker presents a general theory for the computation of stream transformers of the form  $F:(R \to B) \to (T \to A)$ , where the domains T and R for time and A and B for data may be discrete or continuous. The authors show how methods for representing topological algebras by algebraic domains can be applied to transformations of continuous streams. A stream transformer is continuous in the compact-open topology on continuous streams if and only if it has a continuous lifting to a standard algebraic domain

representation of such streams. The chapter also examines the important problem of representing discontinuous streams, such as signals  $T \to A$  where time T is continuous and data A is discrete.

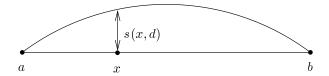

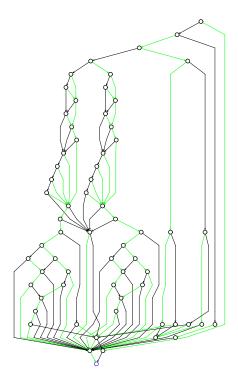

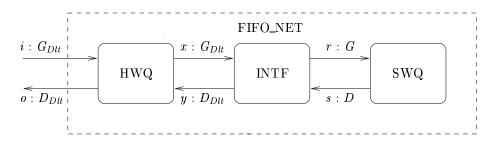

In the chapter *Ideal stream algebra*, B. Möller provides some mathematical properties of *behaviours* of systems, where the individual elements of a behaviour are modeled by *ideals* of a suitable partial order. It is well-known that the associated ideal completion provides a simple way of constructing algebraic cpos. An ideal can be viewed as a set of consistent finite or compact approximations of an object which itself may be infinite. A special case is the domain of streams where the finite approximations are the finite prefixes of a stream. The author defines a number of operators on ideals and behaviours and proves distributivity and monotonicity laws that are the basis for correct refinement of specifications into implementations. Various small examples illustrate that the operators lead to very concise while quite clear specifications. The chapter also gives a characterization of safety and liveness and generalizes the Alpern/Schneider decomposition lemma to arbitrary domains. An extended example concerns the specification and transformational development of an asynchronous bounded queue.

The final chapter of this part, Normalisation by evaluation by U. Berger, M. Eberl and H. Schwichtenberg, deals with a different area of the mathematical foundations of Hardware design. It extends normalization by evaluation from the pure typed $\lambda$ -calculus to general higher type term rewrite systems. This work also gives a theoretical explanation of the normalization algorithm implemented in the verification system MINLOG.

## 4.2 Hardware and Dynamical Systems

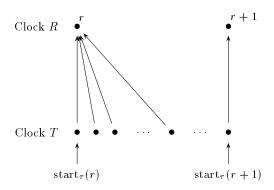

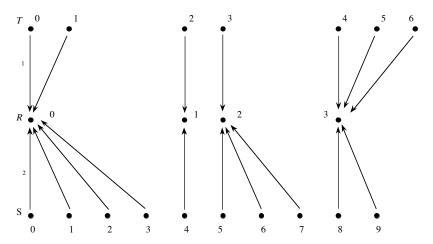

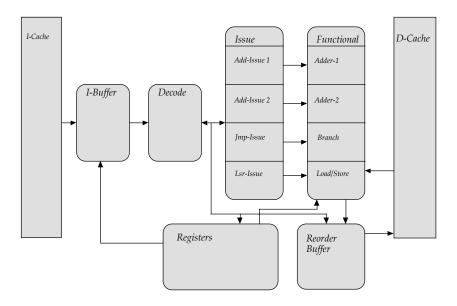

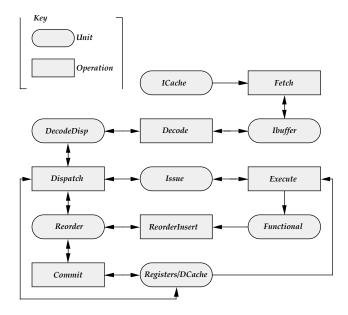

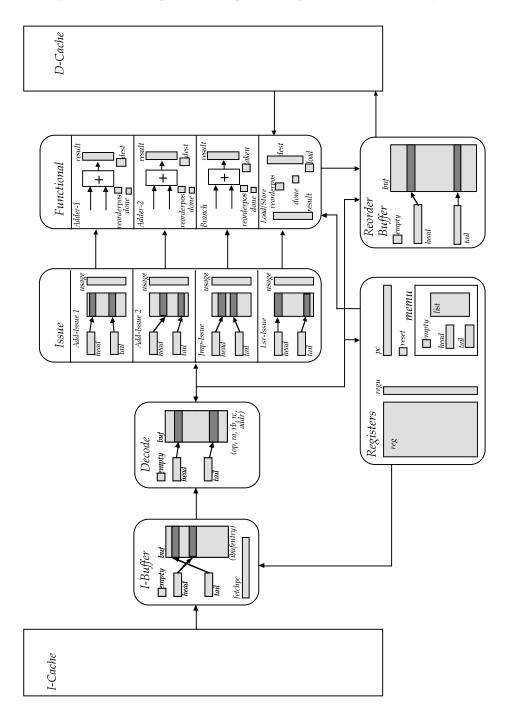

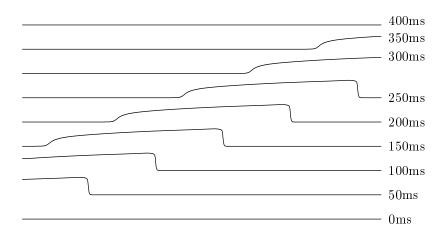

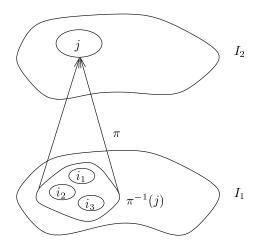

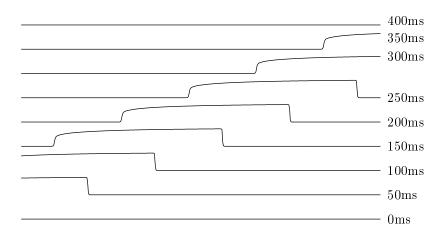

In Algebraic models of superscalar microprocessor implementations: a case study, A.C.J. Fox and N.A. Harman extend a set of algebraic tools for microprocessor specification to model superscalar microprocessor implementations, and apply them to a case study. They develop existing correctness models to accommodate the more advanced timing relationships of superscalar processors, and consider formal verification. They illustrate their tools and techniques with an in-depth treatment of an example superscalar implementation. Clocks divide time into (not necessarily equal) segments, defined by the natural timing of the computational process of a device. The authors formally relate clocks by surjective, monotonic maps called retimings. In the case of superscalar microprocessors, the normal relationship between "architectural time" and "implementation time" is complicated by the fact that events that are distinct in time at the architectural level can occur simultaneously at the implementation level.

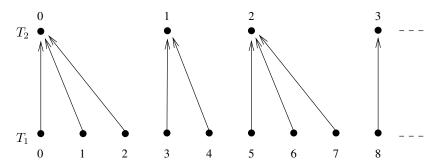

The chapter Hierarchies of spatially extended systems and synchronous concurrent algorithms by M.J. Poole, A.V. Holden and J.V. Tucker takes a very broad view of hardware, including even biological systems. First, the authors study the general idea of a spatially extended system (SES) and argue that many mathematical models of systems in computing and natural science are examples of SESs. They examine the computability and the equational definability of SESs and show that, in the discrete case, there is a natural sense in which

an SES is computable if, and only if, it is definable by equations. The authors look at a simple idea of hierarchical structure for SESs and, using respacings and retimings, define how one SES abstracts, approximates, or is implemented by another SES. Secondly, the authors study a special kind of SES called a synchronous concurrent algorithm (SCA). They define the simplest kind of SCA with a global clock and unit delay which are computable and equationally definable by primitive recursive equations over time. The authors focus on two examples of SCAs: a systolic array for convolution and a non-linear model of cardiac tissue. The chapter investigates the hierarchical structure of SCAs by applying the earlier general concepts for the hierarchical structure of SESs. Th authors apply the resulting SCA hierarchy to the formal analysis of both the implementation of a systolic array and the approximation of a biologically detailed model of cardiac tissue.

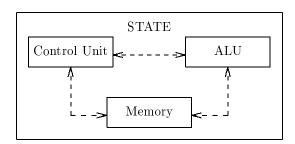

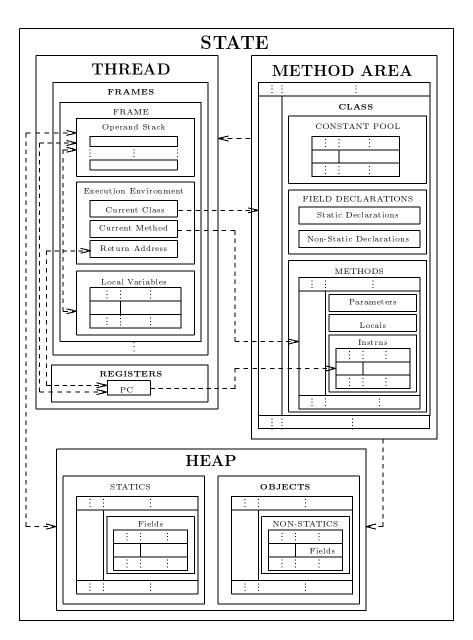

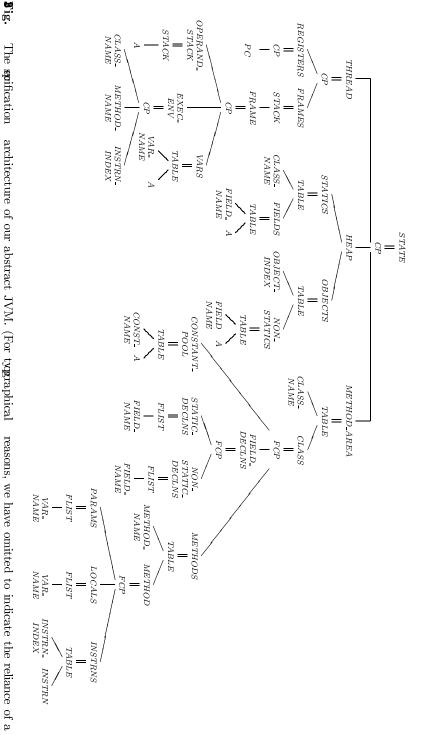

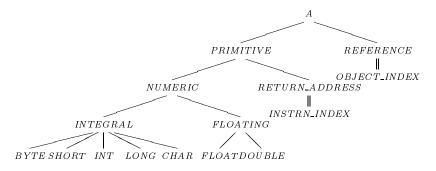

In Towards an algebraic specification of the Java virtual machine K. Stephenson develops an algebraic specification of the architecture of an abstract and simplified version of the Java Virtual Machine (JVM). This concentration on the implementation-independent features of the machine allows her to build a clean and easily comprehensible model in which its structure is emphasized. The author then axiomatizes the semantics of programs on this architecture. She also considers how one can concretize this abstract model which provides a firm foundation for exploring the entire JVM and thus of analyzing the correctness of Java implementations.

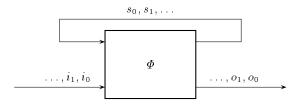

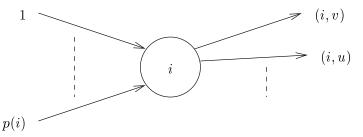

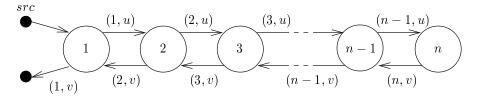

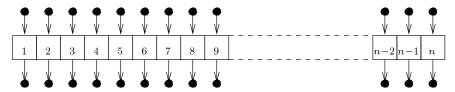

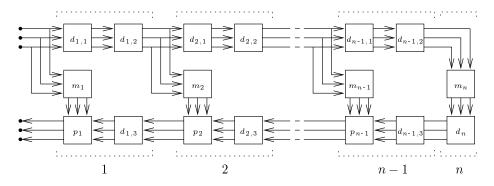

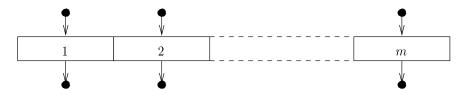

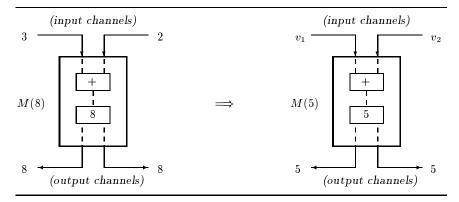

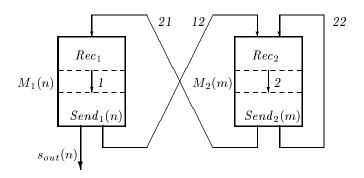

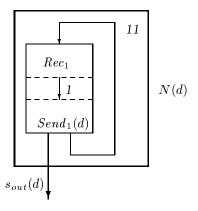

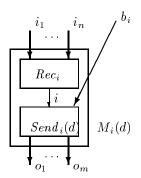

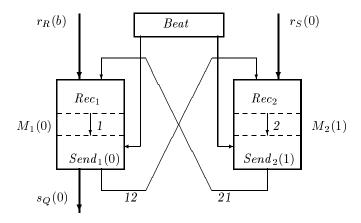

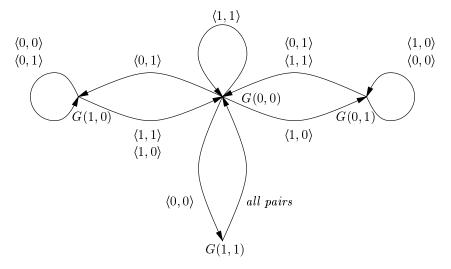

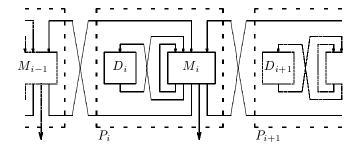

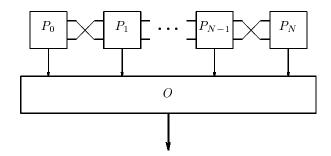

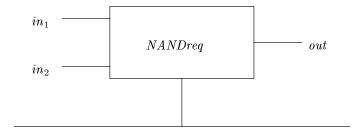

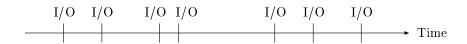

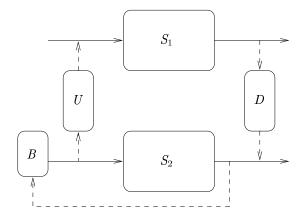

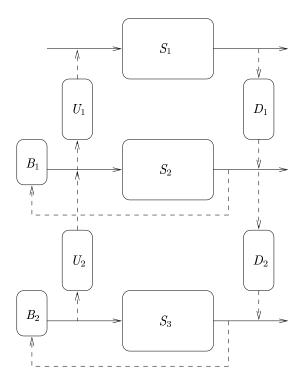

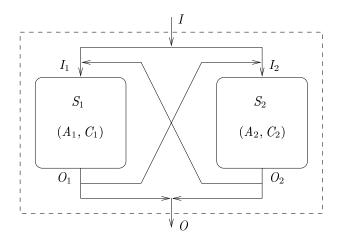

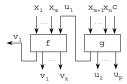

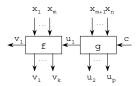

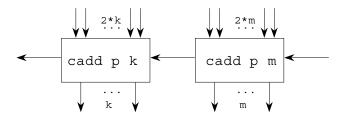

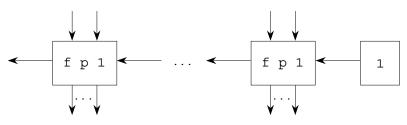

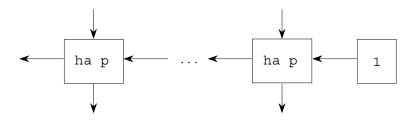

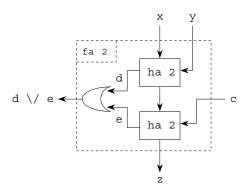

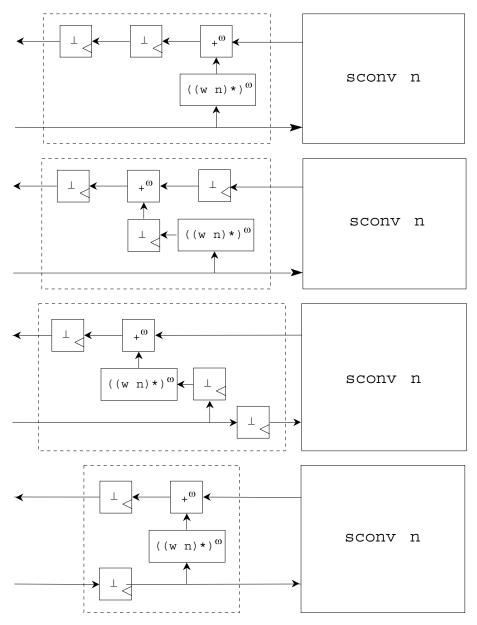

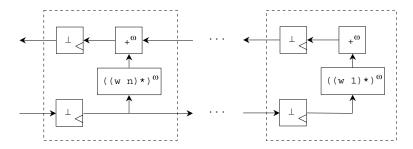

In the next chapter, J.A. Bergstra and A. Ponse study *Grid protocol specifications*. A grid protocol models concurrent computation, and consists of one or more modules repeatedly performing parallel I/O and computation. The authors provide several concise specification formats and correctness results on (external) I/O behaviour and illustrate their approach by examples.

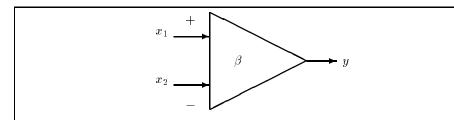

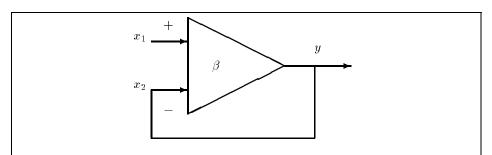

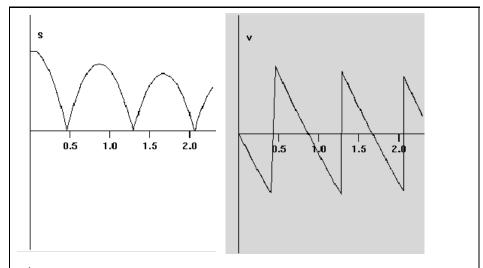

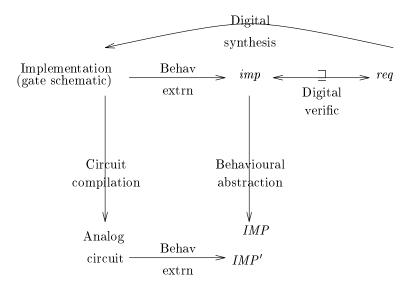

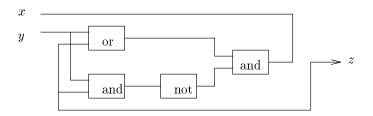

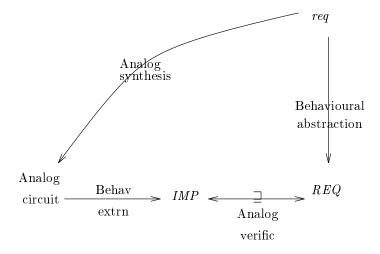

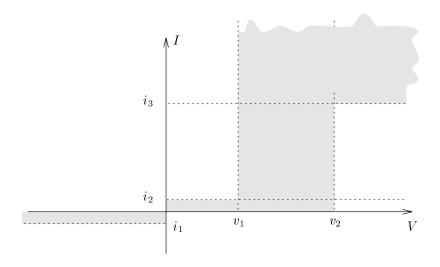

The aim of the chapter The computational description of analogue system behaviour by P.T. Breuer, N. Martínez Madrid and C. Delgado Kloos is to define a simple analogue hardware description language L and give it a sound semantics that supports formal reasoning about its properties. The syntax of L is that of a hybrid programming languages but the semantics has been derived from the analogue signal semantics of the upcoming IEEE VHDL-AMS extension to the IEEE standard digital hardware description language, VHDL. L is here given two semantics. Firstly, what may be termed an exact, or hardware, semantics and, secondly, an approximation, or simulation, semantics. The simulation semantics is computable and the hardware semantics is not. The authors show that the simulation semantics approximates the hardware semantics in a well-defined sense. This property is a "no surprises' guarantee with respect to simulation for the language.

#### 4.3 Verification and Deductive Design

This part starts with *Reasoning about imperfect digital systems* by K. Hanna. The basis of his chapter is the observation that in order to realize digital systems that operate at high speeds or that have very low power consumption, it is necessary

#### 24

to work directly at the analog level of abstraction, that is, in terms of analog electronic components such as resistors and transistors. Although the external behaviour of such circuits can be described digitally, their internal operation can only be explained by working at the analog level and by taking account of both voltages and currents. This chapter describes how existing methods of specification and formal verification of digital systems can be extended so as to encompass such analog designs in a fully rigorous manner.

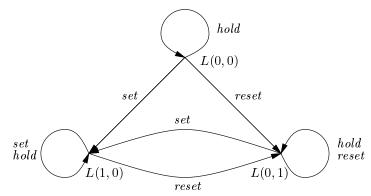

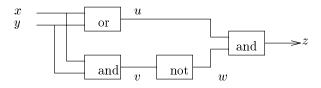

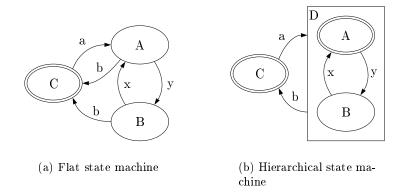

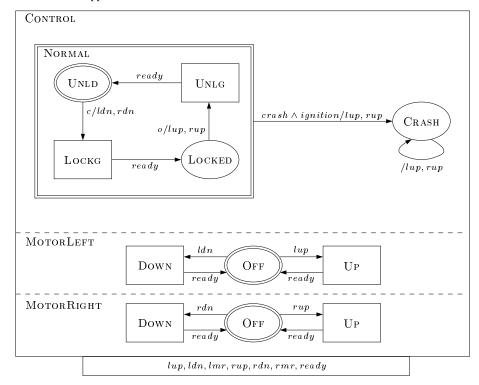

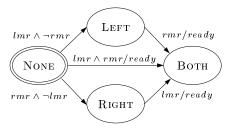

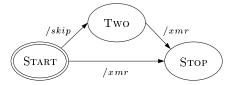

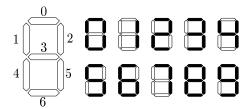

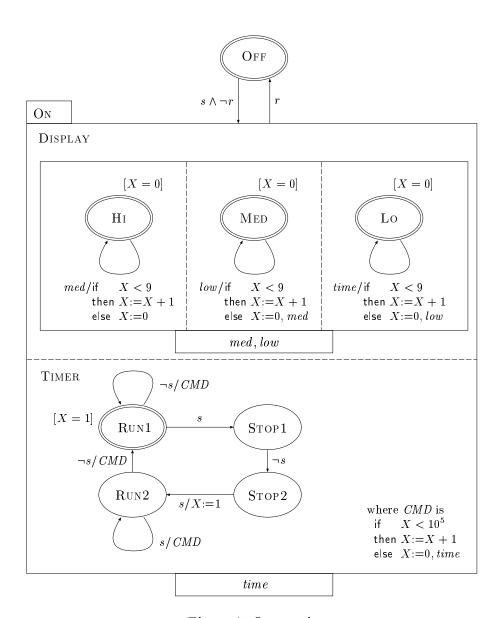

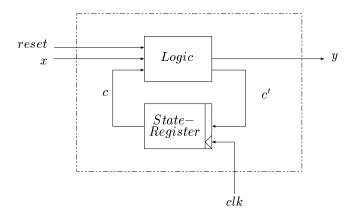

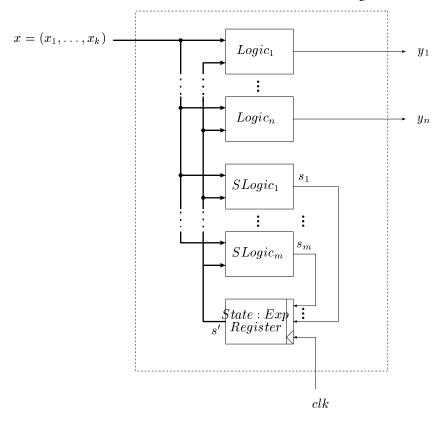

The chapter by J. Philipps and P. Scholz is about Formal verification and hardware design with statecharts. Statecharts extend the concept of Mealy Machines by parallel composition, hierarchy, and broadcast communication. While Statecharts in principle are widely accepted in industry, some semantical concepts, especially broadcasting, are still contested. In this contribution, the authors present a Statechart dialect that includes the basic concepts of the language and present a formal, relational semantics for it. They show that this semantics can be used for both formal verification by model checking and hardware synthesis.